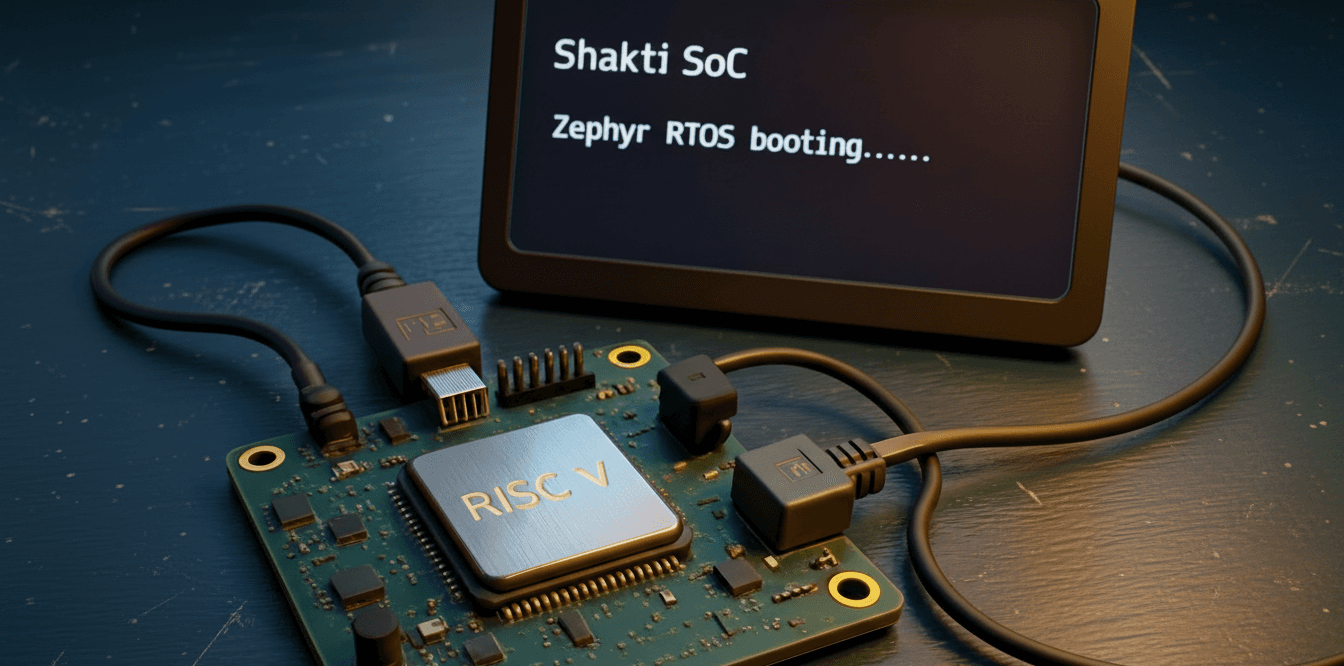

This case study describes the porting of the Zephyr RTOS to the 64-bit Shakti Vajra RISC-V SoC running on the Xilinx Arty A7-100T FPGA. It explains the upgrade from an older 32-bit implementation to a modern 64-bit platform. The work includes board support package development, kernel changes, and UART bring-up. Testing was carried out on both QEMU and FPGA hardware to verify correct operation. The result is a stable real-time operating system platform ready for further development

Zephyr RTOS porting to custom RISC-V based SoC

Zephyr RTOS | Shakti SoC | RISC-V | Arty A7-100T

This case study presents the end-to-end porting of U-Boot and Embedded Linux on the Shakti VAJRA RISC-V SoC implemented on the Xilinx Arty A7-100T FPGA. It details board-specific bootloader customization, UART bring-up, memory mapping, and stable Linux boot integration. The work demonstrates a dual-platform development approach using both QEMU and FPGA hardware to accelerate bring-up and debugging. Key challenges in UART reliability and boot flow stabilization are discussed along with their solutions. The outcome establishes a scalable and robust firmware foundation for future RISC-V research and product development.

U-Boot and Embedded Linux porting to custom RISC-V based SoC

U-Boot | Shakti SoC | RISC-V

The Rust Revolution: Why Embedded Engineering is Changing Forever

Rust | Embedded | Engineering

A Developer's Guide to Mastering Git & GitHub

Git | GitHub